The businesses allow an interoperable coherent optics ecosystem that may assist streamline the event of knowledge middle interconnect and metro transport methods

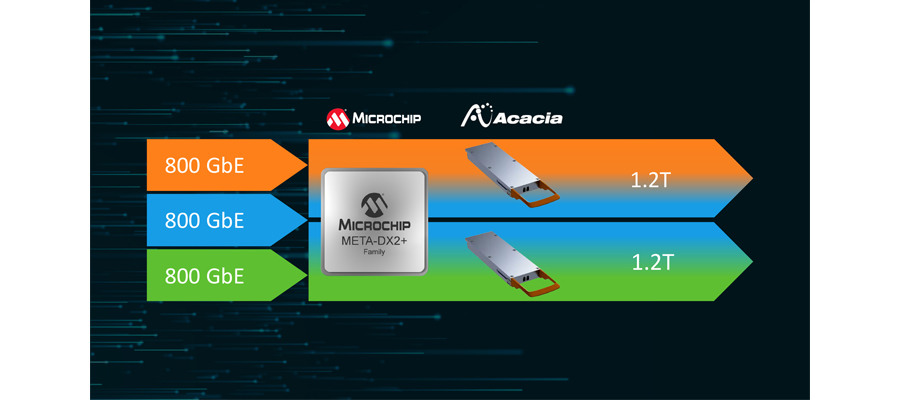

The newest knowledge middle architectures and elevated site visitors are driving larger bandwidth necessities between knowledge facilities. To handle this problem, system builders should streamline the event of a brand new technology of 1.2 Tbps (1.2T) transport options throughout a variety of consumer configurations. This requires that in the present day’s terabit-scale Ethernet PHY units and coherent optical modules interoperate with one another in Knowledge Middle Interconnect (DCI) and metro transport networks. Microchip Expertise in the present day proclaims that it has labored with Acacia to show the fourth technology of interoperability between Microchip’s META-DX2 Ethernet PHY household and Acacia’s Coherent Interconnect Module 8 (CIM 8).

The 2 firms’ interoperable units allow low-power, bandwidth-optimized, scalable options for pluggable optics in DCI and transport networks. They ship three key advantages as they collectively allow high-capacity, multi-rate muxponders for optical transport platforms:

- Optimized DCI bandwidth: The META-DX2 household, by way of its META-DX2+ PHY, makes use of its distinctive Lambda Splitting characteristic to separate 400 GbE or 800 GbE purchasers throughout a number of wavelengths pushed by the CIM 8 modules. This maximizes the capability between knowledge facilities in price configurations reminiscent of 3×800 GbE over 2×1.2 Tbps waves or 5×400 GbE over 2×1.0 Tbps waves.

- Lowered design danger: Microchip and Acacia have collectively verified profitable SerDes interoperation at as much as 112G per lane for Ethernet and OTN purchasers, which reduces design validation and system qualification necessities.

- Higher assist for full bandwidth, multi-rate operation: The META-DX2+ crosspoint and gearbox features allow 100 GbE to 800 GbE consumer modules to attach with full bandwidth to CIM 8 modules.

“This interoperability extends a long-established partnership with Acacia to assist speed up and optimize the build-out of cloud computing and AI-ready optical networks whereas decreasing improvement danger for our prospects,” stated Maher Fahmi, vice chairman for Microchip’s communications enterprise unit. “Our META-DX2 is the primary resolution of its sort to combine 1.6T of encryption, port aggregation and Lambda Splitting into probably the most compact 112G PAM4 gadget out there.”

“With Acacia’s CIM 8 coherent modules verified to interoperate with Microchip’s META-DX2 units, we see this as a sturdy resolution that reduces system time-to-market,” stated Markus Weber, senior director DSP product line administration of Acacia. “The compact dimension and energy effectivity of our CIM 8 coherent modules have been designed to assist community operators deploy and scale capability of high-bandwidth DWDM connectivity between knowledge facilities and all through transport networks.”