- Improves PCIe design productiveness utilizing a better and streamlined workflow with simulation-driven digital compliance take a look at options

- Helps design exploration and report era that speeds chiplet sign integrity evaluation and UCIe compliance verification to extend designer productiveness and time-to-market

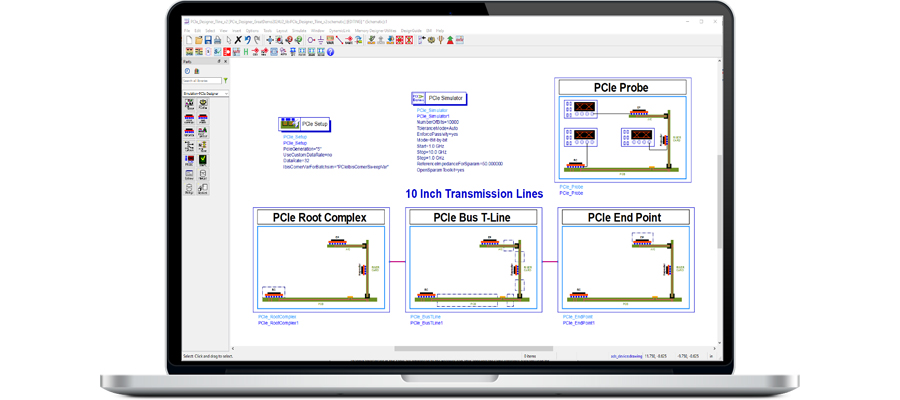

Keysight Applied sciences, Inc. introduces System Designer for PCIe, a brand new product within the Superior Design System (ADS) product suite that helps simulation workflows based mostly on trade requirements for high-speed, high-frequency digital designs. System Designer for PCIe is an clever design atmosphere for modeling and simulating the newest Peripheral Element Interconnect Categorical (PCIe) Gen5 and Gen6 techniques. Keysight can be bettering its digital design automation (EDA) platform by including new options to the present Chiplet PHY Designer software to estimate chiplet die-to-die hyperlink margin efficiency and Voltage Switch Perform (VTF) compliance measurement.

PCIe is a flexible and important interface customary throughout a variety of electronics trade segments on account of its high-speed knowledge switch capabilities, scalability, and flexibility. Adoption spans from on a regular basis shopper electronics to specialised functions in high-performance computing and significant infrastructure techniques.

Advanced PCIe designs assist multi-link and multi-lane techniques that contain a fancy evaluation setup between RootComplex and Finish-Level, generally incorporating mid-channel repeaters. Designers spend an inordinate period of time making ready simulations which can be susceptible to errors. Simulations usually lack vendor-specific algorithmic modeling interface (AMI) simulation fashions, that are required early within the design cycle for design house exploration. Designers additionally want assurance that their prototype design will go compliance testing earlier than {hardware} fabrication.

Productiveness, Workflow, and Compliance Enchancment Options

- The System Designer for PCIe automates the setup for multi-link, multi-lane, and multi-level (PAM4) PCIe techniques utilizing a sensible design atmosphere. It simplifies simulation setup and reduces time-to-first-insight.

- The PCIe AMI modeler, which helps NRZ and PAM4 modulations, facilitates fast AMI mannequin era wanted for PCIe system evaluation. The AMI Mannequin Builder offers designers a wizard-driven AMI mannequin era workflow to quickly create fashions for each transmitters (Tx) and receivers (Rx).

- Streamlined, simulation-driven digital compliance testing permits designers to make sure design high quality. The built-in, simulation-driven PCIe compliance take a look at workflow reduces design prices by minimizing design iterations and shortening time-to-market.

Chiplet PHY Designer Enhancements

- Chiplet PHY Designer is the EDA trade’s first simulation answer for Common Chiplet Interconnect Categorical (UCIe) requirements, enabling predictions of die-to-die hyperlink margin, VTF for channel compliance evaluation, and forwarded clock functionality. Chiplet PHY Designer consists of new design exploration and report era options that speed up sign integrity evaluation and compliance verification to enhance designer productiveness and time-to-market.

Hee-Soo Lee, Director of Excessive-Velocity Digital phase, Keysight EDA, mentioned, “We proceed to broaden our standards-driven workflow method to assist our clients. Our high-speed digital product portfolio is main the EDA trade with probably the most correct and superior simulation software program for sign integrity evaluation and compliance take a look at validation. Digital requirements corresponding to PCIe and UCIe are important to the efficiency of digital techniques. Designers utilizing our PCIe and UCIe simulation options of their workflows can shift left their improvement cycle to avoid wasting vital time and value.”