We current a Focus problem on how the analysis neighborhood is frequently pushing the gadget efficiency boundaries of 2D transistors and discover the pivotal function that these gadgets play sooner or later computing panorama.

On the 2024 System Analysis Convention (https://2024.deviceresearchconference.org/), held in June in Faculty Park, MD, there was a powerful emphasis on the crucial function of semiconductor expertise in powering the huge adoption of synthetic intelligence (AI). With huge parallel processing and specialised accelerators, graphics processing models (GPUs) and tensor processing models (TPUs) have change into workhorses for information crunching and machine studying, powering cutting-edge purposes. Nevertheless, a serious looming problem is the best way to break by the silicon ceiling’s limitations on transistor scaling and energy consumption to maintain fast AI {hardware} efficiency features. The reply lies in rethinking gadget structure and exploring different supplies. Amongst them, two-dimensional (2D) supplies have proven nice potential to push the boundaries of semiconductor gadget efficiency and performance. A lot of the analysis in 2D supplies printed in our journal displays this upward development and, on this problem, we current a Focus that highlights advances in 2D semiconductors, leveraging nanoscale insights to design novel gadgets, enhance efficiency, and allow built-in programs.

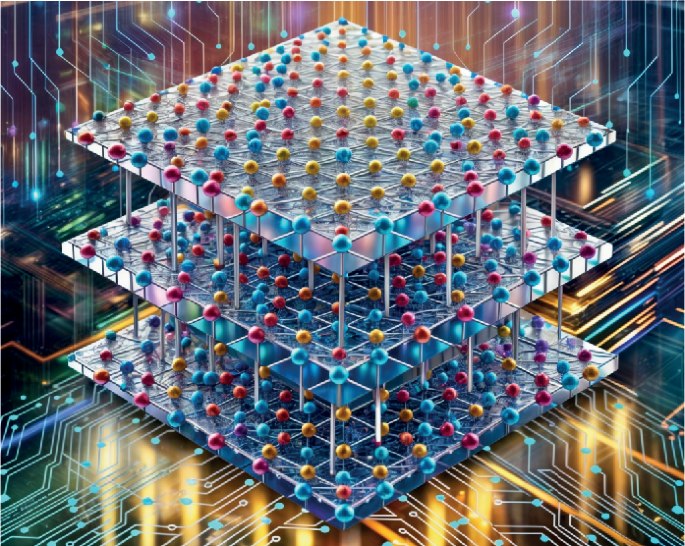

Credit score: Subir Ghosh and Saptarshi Das

In an Evaluation, Yu-Cheng Lu et al. use expertise computer-aided design to match 2D- and Si-based static random-access reminiscence (SRAM) circuits throughout varied expertise nodes, from 16 nm to 1 nm. Because the node will get smaller, the 2D-based SRAM outperforms its silicon counterparts when it comes to stability, working pace, and vitality effectivity.

Scaling high-quality 2D supplies with silicon-like manufacturing stays a key problem to leveraging their superior semiconductor efficiency. Regardless of the wealth of printed recipes and methodologies, the dearth of hands-on, shop-floor experience hinders constant high-quality materials synthesis. Of their Assessment, Can Liu et al. talk about epitaxial progress of in-plane single-crystal monolayers and the fabrication of out-of-plane homostructures. By analysing nucleation and orientation management in addition to the defect stage with varied epitaxial progress methods, they talk about finest practices to constantly produce high-quality 2D supplies.

In one other Assessment, Ki Seok Kim et al. illustrate an idealized 2D transistor, specializing in channel supplies, steel contacts, and gate dielectrics, and share their view on methods to bridge the hole between tutorial analysis and industrial must speed up the adoption of 2D semiconductor-based transistors for monolithic 3D integration.

The Focus additionally options main analysis advancing 2D transistor efficiency limits. Of their Article, Kui Meng et al. report wafer-scale thermal evaporation of superionic rare-earth-metal fluoride movies with ultrathin equal oxide thickness as dielectrics in MoS2 and WSe2 transistors. In contrast to electrostatic gating, these electric-double-layer gated transistors use ions to induce cost within the transistor channel. This answer may very well be efficient in purposes that don’t require excessive operational frequencies, comparable to neuromorphic or stochastic computing, as highlighted by Tibor Grasser et al. in a Information & Views article.

Additional size-scaling on the gate electrode is exemplified in an Article by Heonsu Ahn et al. They fabricate mirror twin boundary networks with a 0.4-nm-width gate electrode to scale the depletion channel size down to three.9 nm. Earlier profitable implementations of atomically brief gate transistors used carbon nanotubes or graphene edges. An accompanying Information & Views article by Wouter Jolie et al. featured this strategy that streamlines the manufacturing course of by using the identical 2D materials for wiring and as an lively semiconductor.

Forming electrical contacts with 2D transistors includes overcoming challenges widespread to creating ohmic contacts with standard semiconductors, like Schottky obstacles and Fermi stage pinning. Of their Article, Jordan Pack et al. current a brand new sort of charge-transfer-contact to mitigate these points, acquiring a record-high mobility (80,000 cm2 V–1 s–1) of monolayer WSe2 at low temperature.

Substantial efforts have been invested in shifting from particular person gadgets to the system stage as effectively. A back-end-of-line compatibility strategy to construct complementary steel–oxide–semiconductor gadgets on 2D supplies is offered by Rahul Pendurthi et al. of their Article.

In 2022, the US authorities handed the influential CHIPS and Science Act to help semiconductor analysis and manufacturing. In the meantime, governments in Asia and Europe are additionally rolling out their very own variations of the CHIPS and Science Act, providing substantial subsidies for semiconductor R&D and manufacturing. Expertise and geopolitics are more and more intertwined, as articulated within the New York Instances bestseller Chip Conflict by Chris Miller. The battle for technological primacy dangers making data trade and expertise switch amongst scientists more and more difficult.

As a journal with world attain, we worth the free movement of information sharing with this Focus and can proceed to comply with how each step taken within the laboratory aligns with the wants of the business. Our function as a journal is to supply a well-curated platform for the open sharing of concepts, methodologies, and breakthroughs, transcending these geopolitical divides to advocate that the development of semiconductor expertise stays a collaborative world endeavour.